# Intel® Dialogic® DMV160LP

# 16-Port, PCI-based DM3 Voice Processing and Analog Interface Board

Part of the next-generation family of Intel® Dialogic® analog PCI boards, the DMV160LP is a 16-port, PCI-based voice processing and analog interface board offering the enhanced capabilities a competitive communications market segment demands.

#### **Features and Benefits**

**High density:** With 16 ports, the DMV160LP lets you design high-density, state-of-the-art PCI messaging solutions, lowering costs while building bigger systems with fewer boards per chassis. Sixteen independent loop-start telephone interfaces and 16 channels of voice processing in one PCI slot provide effective solutions for building high-density analog applications.

**International approvals:** Widespread International approvals increase your market segment opportunities by allowing you to deploy your solution worldwide. Full support for Japanese Caller ID, including the ability to detect on-hook polarity reversals, provides accurate and reliable CID information.

**Value:** Simultaneous voice with CSP and fax capability in the same application, available for the first time on an Intel® analog loop-start board, enhance system value and flexibility.

**Standards-based:** Full-size PCI form factor is compatible with industry standards, providing H.100 media-sharing support.

**Ideal for multitasking:** Voice with Continuous Speech Processing (CSP) and fax capability ensures server efficiency in multi-tasking environments.

**State-of-the-art voice compression:** Advanced low-bit-rate coders, including TrueSpeech\*, help preserve hard disk space and reduce system loading.

**Flexible:** Programmable Automatic Gain Control (AGC) parameters offer developers greater flexibility for implementing and installing highly accurate, mission-critical voice processing systems.

Efficient: Four ports of on-board fax save money and give developers more resources without using additional chassis slots or hardware.

**Saves processing resources:** CSP allows the board to offload to the host processor critical real-time signal processing in speech-enabled applications. This reduces system cost and latency, increases recognition accuracy, and improves overall system response time for high-density speech solutions.

Choice of operating systems: Support for Windows NT, Windows 2000, and Windows XP operating systems ensures high reliability in multitasking environments. (RedHat\* Linux\* support is planned to be available in a future release.)

Simple to deploy: Universal 32-bit PCI edge connector ensures compatibility with 3.3 volt and 5.0 volt bus signals, enabling simpler deployment in a wide variety of PCI chassis from popular manufacturers.

**Easy to add features:** DM3 downloadable signal and call processing firmware provide easy feature enhancement and field-proven performance.

### Intel in Communications

Ideal for advanced computer telephony (CT)-based communications applications that require multimedia resources, this high-performance, scalable board offers a rich set of advanced features and support for state-of-the-art digital signal processing (DSP) technology and signal processing algorithms ensuring a competitive edge for your solutions.

With its advanced features and technologies, the DMV160LP is well suited as the principal building block for developing multimedia communications applications including Web-enabled contact centers, unified messaging, and speech-enabled interactive media response (IMR) systems. Plus, with widespread global approvals, the DMV160LP allows you to take your solutions into the global marketplace. It also supports caller ID in the U.S., Japan, and the U.K. A special version of the board is available for deployment in the European Union.

This full-size, universal PCI, loop-start board offers 16 analog telephony ports for high-density analog voice processing solutions. It is compatible with the Windows\* 2000, Windows NT\*, and Windows XP\* operating systems. (RedHat\* Linux\* operating system compatibility is planned to be available in a later release.) It is based on the Intel® DM3 mediastream architecture, which provides a development environment that accelerates application development and provides a path for future growth. Because of support for the Intel® R4 application programming interfaces (APIs), DM3-based boards easily interoperate with other Intel CT Bus and SCbus boards. Applications can be easily ported to lower- or higher-density platforms and new features can be added with only minimal modification, protecting investments in hardware and application code.

CT Bus compatible, the DMV160LP also includes Continuous Speech Processing (CSP), a set of software and firmware features that support high-performance speech-enabled applications. Other key features for designing enhanced voice processing systems include Automatic Gain Control (AGC), call progress analysis,

and transaction record. The DMV160LP also features advanced coders including TrueSpeech\* and four ports of on-board DSP-based fax.

Advanced features include new voice coders, including G.726 and GSM, for complying with Voice Profile for Internet Messaging (VPIM) standards. Software-based fax and host-based speech recognition let developers add robust enhancements without having to add hardware. With the support of the industry-standard PCI bus architecture and the international standard TBR21 in a single board, developers can incorporate the DMV160LP board into solutions with unmatched price/performance.

Intel voice products offer a rich set of advanced features, including state-of-the-art DSP technology and signal processing algorithms, for building the core of any converged communications system. With industrystandard PCI bus expansion boards, developers can easily and cost effectively integrate Intel voice products into exactly the type of system they need — enjoying superior performance.

# **Configurations**

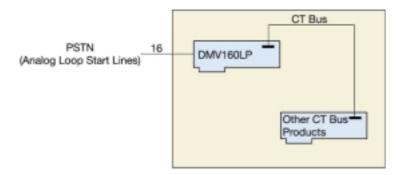

Use the DMV160LP board to build sophisticated CT systems incorporating capabilities such as speech recognition, facsimile, and text-to-speech (TTS). The DMV160LP board shares a common hardware and firmware architecture with other Intel® CT Bus- and SCbus based boards for maximum flexibility and scalability. (See Figure 1.)

Add features or grow the system while protecting your investment in hardware and application code.

The DMV160LP board provides 16 channels of call processing and loop start interfaces in a single PCI slot. The unique dual-processor architecture, comprised of DSPs and a general-purpose microprocessor, handles all telephony signaling and performs all DTMF (touchtone) and audio/voice signalprocessing tasks. Each board also includes four ports of fax functionality.

#### **Applications**

- Voice Mail/Voice Messaging

- Interactive voice response (IVR)

- Contact Center

- Unified Messaging

- Dictation

Figure 1: DMV160LP Configuration Diagram

The DMV160LP board supports simultaneous voice with CSP and fax processing in the same application. This provides greater flexibility in applications processing. Downloaded firmware algorithms including DM3 provide variable voice coding at 24 and 32 kb/s ADPCM, and 48 and 64 kb/s µ-law or A-law PCM, and MS-WAVE 8 bit linear - 88 kb/s.

For advanced messaging applications, new low-bit-rate coders are also available including GSM at 13 kb/s, G.726 at 32 kb/s, and TrueSpeech\* at 8.5 kb/s. Sampling rates and coding methods are channelby-channel selectable. Applications can dynamically switch the sampling rate and coding method to optimize data storage or voice quality as needed. DM3 firmware provides reliable DTMF detection, DTMF cut-through, and talk-off/play-off suppression over a wide variety of telephone line conditions.

# Software Support

The DMV160LP board is currently supported by the Intel® Dialogic® System Release (SR) software and software development kits (SDKs) for the Windows NT, Windows 2000, and Windows XP operating systems. These packages contain tools for developing complex multichannel applications.

The DMV160LP DSP-based fax interface is designed to work consistently with the Intel® System Release 5.1.1 feature pack 1 (and subsequent releases) voice and call processing interfaces.

Global Call, a high-level call control utility, simplifies the development and use of compelled R2 and other special signaling protocols.

# **Functional Description**

The DMV160LP board connects 16 analog loop start telephone lines to 16 onboard call processing resources or to other resources via the CT Bus. The 16 analog network interfaces use low-profile, integrated line isolation circuits that detect ringing, seize the line, and couple bidirectional voice signals. Discrete circuits provide detection of loop polarity and off-hook line status. This product presents either a 600 Ohm nominal or regulatory-required complex impedance load to the subscriber line (DMV160LPEU). The DMV160LP uses standard R4 for DM3 host software as distributed in the PCI Windows System Release.

This board provides a 33 MHz-compliant, 32 bit target PCI (Rev. 2.2) bus interface. The PCI system bus interface on this board complies with universal board requirements. The PCI bus drives the bus signals in accordance with the voltage applied to the PCI bus VIO pins. The PCI system bus is a 32 bit, hot plugcompatible interface.

This board provides:

- Class B EMI suppression, FCC class A compliant

- Ring, loop current, polarity detection, and on-hook/off-hook signaling control via Global Call

- Tone detection and generation

- On-hook audio path

- Digitization and playback of voice files

The signals from the 16 loop start telephone lines connected to the DMV160LP board first pass through a telephone line interface that provides transient protection and electromagnetic interference (EMI) suppression. These telephone line interfaces use reliable, solid-state hook switches (no mechanical contacts) and FCC-Part 68 Class A ring voltage and

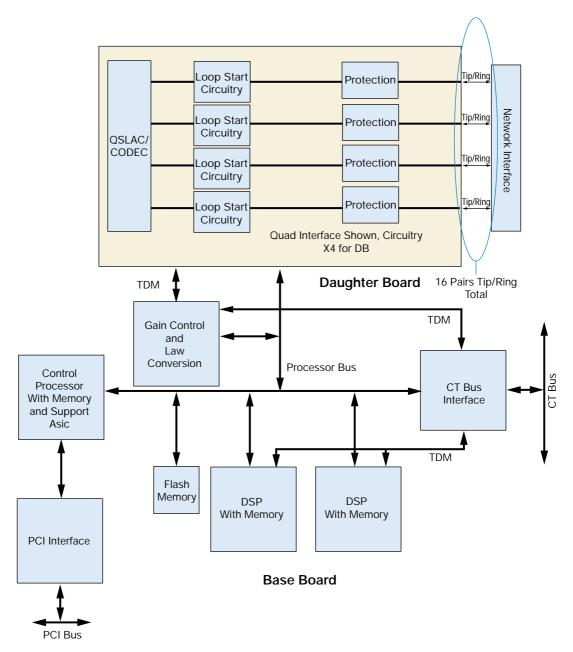

Figure 2: DMV160LP Hardware Block Diagram

Class B ring frequency circuitry. Each interface incorporates circuitry that protects against high-voltage spikes and adverse network conditions and allows applications to go off-hook any time during ring cadence without damaging the board.

The digitized voice signals are routed via the CT Bus either to an onboard DSP or to an external resource on any of the 4096 CT Bus time slots. This enables the application to reroute calls to any added system resource, such as a speech recognition, facsimile, or text-to-speech (TTS) board.

Part of the DMV160LP board's telephone interface includes an on-hook audio path that detects Caller ID information. Depending on the level of service offered by the local telephone provider, Caller ID can include the date, time, caller's telephone number, and the name of the person calling (in some enhanced Caller ID environments). The on-hook audio path can also detect touch-tones while the line is on-hook. This capability lets developers use the DMV160LP board behind PBXs that require on-hook touchtone detection for signaling.

When the onboard call processing resources are used, the network signals are extracted and passed to the onboard control processor, which can change channel status and communicate channel events to the application interface via a shared RAM and the host PC PCI bus.

On voice playback, the DSP sends the digitized voice samples to the CODEC function, which is provided by 2 QSLAC chips. The CODEC codec converts the digitized voice into analog voice and sends the voice response to the caller via the telephone line interface.

When the system is initialized, DM3 firmware is downloaded from the host PC to the board. DM3 firmware controls all board operations and gives the board all of its intelligence and enables easy feature enhancements and upgrades.

The onboard control processor controls all operations of the DMV160LP board via a local bus and interprets and executes commands from the host PC. This processor handles real-time events, manages data flow to the host PC to provide faster system response time, reduces PC host processing demands, processes DTMF and telephony signaling before passing them to the application, and frees the DSPs to perform signal processing. Communication between the processor and the host PC is via shared RAM, which acts as an input/output buffer to increase the efficiency of disk file transfers. This RAM interfaces to the host PC via the PCI bus. All operations are interrupt-driven to meet the demands of real-time systems. The Board Locator Technology circuit operates in conjunction with a rotary switch that eliminates the need to set confusing jumpers or DIP switches. (See Figure 2.)

# Technical Specifications\*\*

| Technical Specifi  | cations**                        |                                                                                                                                                     |

|--------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | Analog interfaces                | 16                                                                                                                                                  |

|                    | Max. boards/system               | 8 (Number may be limited by application, system performance or memory and number of calls.)                                                         |

|                    | Control microprocessor           | ARM7 RISC processor                                                                                                                                 |

|                    | Control microprocessor memory    | Up to 8 MB local to control processors                                                                                                              |

|                    | Digital signal processors (DSPs) | Motorola* 56311-150 MHz                                                                                                                             |

|                    | DSP memory                       | 512 K word SDRAM local to each DSP<br>ARM ASIC contains internal 1k × 32 bits<br>24-bit wide SRAM local to each DSP                                 |

|                    | Baseboard global memory          | 32-bit wide DRAM accessible to all signal processors and control processor                                                                          |

| PCI Platform       |                                  |                                                                                                                                                     |

|                    | Form factor                      | PCI long card, single-slot width                                                                                                                    |

|                    | Host interface memory            | 33Mhz                                                                                                                                               |

|                    | Bus compatibility                | PCI Bus Specification, Rev. 2.1                                                                                                                     |

|                    | Bus mode                         | Target and DMA master mode operation                                                                                                                |

|                    | Computer telephony bus           | ECTF H.100 compliant CT Bus, offering                                                                                                               |

|                    |                                  | Onboard switching access to 4096 bidirectional 64 kb/s DS0 time slots SCbus interoperability through provided adapter 68-pin ribbon cable connector |

|                    | Telephony bus connector          | H.100-style 68-pin fine pitch card edge connector                                                                                                   |

|                    | Network connectors               | 6 RJ-25 on rear bracket                                                                                                                             |

|                    | Host interface memory            | 512 KB shared with control processor                                                                                                                |

| Power Requirements |                                  |                                                                                                                                                     |

| ·                  | +5 VDC                           | 7.5 W                                                                                                                                               |

|                    | +12 VDC                          | 1.2 W                                                                                                                                               |

|                    | –12 VDC                          | 1.2 W                                                                                                                                               |

|                    | +3.3 VDC                         | Not required                                                                                                                                        |

|                    | Operating temperature            | 0°C to +50° C. Cooling condition per maximum operating temperature                                                                                  |

|                    | Storage temperature              | -20°C to +70°C                                                                                                                                      |

|                    | Humidity                         | 8% to 80% noncondensing                                                                                                                             |

|                    |                                  |                                                                                                                                                     |

# **Resource Technical Specifications\*\***

| Audio Signal     |                                   |                                                                                                                                                                 |

|------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | Usable receive range              | -40 dBm0 to 0 dBm0 nominal, configurable by parameter <sup>†</sup>                                                                                              |

|                  | Automatic gain control            | Application can enable/disable. Above -21 dBm results in full scale recording, configurable by parameter.                                                       |

|                  | Silence detection                 | -40 dBm nominal, software adjustable <sup>†</sup>                                                                                                               |

|                  | Transmit level (weighted average) | -9.5 dBm nominal, configurable by parameter <sup>†</sup>                                                                                                        |

|                  | Transmit volume control           | 20 dB adjustment range, with application-definable increments and legal limit cap                                                                               |

|                  | File data formats                 | TIFF/F (Tagged Image File Format) for transmit/receive MH, MR, and MMF w/ECM                                                                                    |

| Frequency Respor | nse (G.711 PCM Encoding)          |                                                                                                                                                                 |

|                  | 24 Kb/s                           | 300 Hz to 2600 Hz ±3 dB                                                                                                                                         |

|                  | 32 Kb/s                           | 300 Hz to 3400 Hz ±3 dB                                                                                                                                         |

|                  | 64 Kb/s                           | 300 Hz to 3400 Hz ±1 dB                                                                                                                                         |

| Audio Digitizing |                                   |                                                                                                                                                                 |

|                  | TrueSpeech                        | 8.5 kb/s                                                                                                                                                        |

|                  | G.726                             | OKI ADPCM @ 6 kHz sampling                                                                                                                                      |

|                  | GSM                               | 13 kb/s ETSI 6.10 full rate                                                                                                                                     |

|                  | Linear PCM                        | 88 kb/s @ 11 kHz sampling rate, 8 bits sample                                                                                                                   |

|                  | ADPCM: 24 kb/s                    | OKI ADPCM @ 6 kHz sampling rate                                                                                                                                 |

|                  | ADPCM: 32 kb/s                    | OKI ADPCM @ 8 kHz sampling rate                                                                                                                                 |

|                  | μ-law or A-law: 48 kb/s           | G.711 PCM @ 6 kHz sampling rate                                                                                                                                 |

|                  | μ-law or A-law: 64 kb/s           | G.711 PCM @ 8 kHz sampling rate                                                                                                                                 |

|                  | Digitization selection            | Selectable by application on function call-by-call basis Pitch controlled                                                                                       |

|                  | Playback speed control            | Available for 8 KHz coders Adjustment range: ±50% Adjustable through application or programmable DTMF control                                                   |

| DTMF Tone Detec  | tion                              |                                                                                                                                                                 |

|                  | DTMF digits                       | 0 to 9, *, #, A, B, C, D per Bellcore LSSGR Sec. 6                                                                                                              |

|                  | Dynamic range                     | -36 dBm to +3 dBm per tone, configurable by parameter <sup>†</sup>                                                                                              |

|                  | Minimum tone duration             | 40 ms; can be increased with software configuration                                                                                                             |

|                  | Interdigit timing                 | Detects like-digits with a >45 ms interdigit delay                                                                                                              |

|                  |                                   | Detects different digits with a 0 ms interdigit delay                                                                                                           |

|                  | Acceptable twist                  | Meets Bellcore LSSGR Sec 6 and EIA 464B requirements                                                                                                            |

|                  | Noise tolerance                   | Meets Bellcore LSSGR Sec 6 and EIA 464B requirements for Gaussian, impulse, and power line noise tolerance                                                      |

|                  | Cut-through                       | Local echo cancellation permits 100% detection with a >4.5 dB return los line                                                                                   |

|                  | Talk off                          | Detects less than 10 digits while monitoring Bellcore TR-TSY-000763 standard speech tapes (LSSGR requirements specify detecting no more than 470 total digits). |

Detects 0 digits while monitoring MITEL speech tape #CM 7291.

## Resource Technical Specifications\*\* (cont.)

| Glo | obal | Tone | Detection |

|-----|------|------|-----------|

|     |      |      |           |

Tone type Programmable for single or dual

Max. number of tones Application-dependent

Frequency range Programmable within 300 Hz to 3500 Hz Max. frequency deviation Programmable in 5 Hz increments

Frequency resolution ±5 Hz. Separation of dual frequency tones is limited to 62.5 Hz at a

signal-to-noise ratio of 20 dB.

Programmable cadence qualifier, in 10 ms increments Timing Dynamic range Default: -38 to -3 dBm, adjustable by parameter file.

Global Tone Generation

Tone type Generate single or dual tones

Programmable within 200 Hz to 4000 Hz Frequency range

Frequency resolution 1 Hz

10 ms increments Duration **Amplitude** 0 to -40 dBm

MF Signaling (T-1)

R1

MF digits 0 to 9, KP, ST, ST1, ST2, ST3 per Bellcore LSSGR Sec 6, TR-NWT-000506

and CCITT Q.321

Transmit level Complies with Bellcore LSSGR Sec 6, TR-NWT-000506 Complies with Bellcore LSSGR Sec 6, TR-NWT-000506 Signaling mechanism

Dynamic range for detection -25 dBm0 to -3 dBm0 per tone

Acceptable twist 6 dB

Acceptable freq. variation Less than ±1 Hz

Call Progress Analysis

Busy tone detection Default setting designed to detect 74 out of 76 unique busy/congestion

tones used in 97 countries as specified by ITU-T Rec. E., Supplement #2. Default uses both frequency and cadence detection. Application can select frequency only for faster detection in specific environments.

Default setting designed to detect 83 out of 87 unique ring back tones Ring back detection

used in 96 countries as specified by ITU-T Rec. E., Supplement #2. Uses

both frequency and cadence detection.

Positive voice detection accuracy

Positive voice detection speed

Positive answering machine detection

accuracy

>98% based on tests on a database of real world calls

Detects voice in as little as 1/10 of 1 second

>85% based on application and environment

Fax/modem detection Preprogrammed

Detects entire sequence of the North American tri-tone. Other intercept Intercept detection

tone sequences can be programmed.

Dial tone detection before dialing Application enable/disable

Supports up to three different user-definable dial tones

Programmable dial tone drop out debouncing (when not part of regulatory

approval)

# Resource Technical Specifications\*\* (cont.)

| Tone Dialing |                         |                                                                               |  |

|--------------|-------------------------|-------------------------------------------------------------------------------|--|

| ŭ            | DTMF digits             | 0 to 9, *, #, A, B, C, D per Bellcore LSSGR Sec. 6, TR-NWT-000506, ITU-T Q.23 |  |

|              | Frequency variation     | Less than ±1 Hz                                                               |  |

|              | Rate                    | 10 digits/s, configurable by parameter <sup>†</sup>                           |  |

|              | Level                   | -4.0 dBm per tone, nominal, configurable by parameter <sup>†</sup>            |  |

|              | Pulse dialing           | 10 PPS standard, 63% break-ratio, configurable by country parameter           |  |

| Protocols    |                         |                                                                               |  |

|              | Analog                  | Loop-start                                                                    |  |

| Facsimile    |                         |                                                                               |  |

|              | No. ports               | 4                                                                             |  |

|              | Compatibility           | Group III SoftFax                                                             |  |

|              | Compression             | ETSI NET30 and ITU-T T.30, T.4, and T.6 compliant MH, MR, MMR and ECM support |  |

|              | Speed                   | 14.4 kb/s or greater, transmit and receive                                    |  |

|              | Fax resource management | Not required                                                                  |  |

### Order by Model Name

- DMV160LP (Approved for use in the US, Canada & International countries excluding the European Union)\*

- DMV160LPEU (Approved for use in countries of the European Union only)\*

- \* Note: No connection or test cables are shipped with the board. Order the Adapter Cable listed below if the developer is not designing a custom cable.

# **Hardware System Requirements**

- Intel® Pentium® III or higher class IBM PC AT PCI bus or compatible computer recommended

- Operating system and memory requirements vary according to the total number of channels being used per system.

# **Optional Components**

# Multi-Drop CT Bus Cables

Component level package options include:

- CTBus-to-SCbus Adapter: 99-2446-001 CTBUSTOSCBUSADP

- CTBus Cable Assembly, 4 drop: 86-0149-004 CBLCTB68C4DROP

- CTBus Cable Assembly, 8 drop: 86-0149-008 CBLCTB68C8DROP

- CTBus Cable Assembly, 12 drop: 86-0149-012 CBLCTB68C12DROP

- CTBus Cable Assembly, 16 drop: 86-0149-016 CBLCTB68C16DROP

## **Adapter Cable**

- Order by model name: CBL6RJ25TORJ21X

- This is a 6PLUG(6P6C)-to-RJ21X (PLUG) connector

Note: No connection or test cables are shipped with the board. Order the Adapter Cable listed below if the developer is not designing a custom cable.

# **Universal Break-Out Box for Lab Environment**

- Order by model name: BOB25POSJ11

- This is a 25RJ11 RJ21X (M&F) WIRED break-out box

To learn more, visit our site on the World Wide Web at www.intel.com

1515 Route Ten Parsippany, NJ 07054 Phone: 1-973-993-3000 Fax: 1-973-993-3093

Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel® products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel® products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice.

\*Other names and brands may be claimed as the property of others.

\*\*All specifications are subject to change without notice.

†Configurable to meet country-specific PTT requirements. Actual specification may vary from country to country for approved products.

Intel, Intel Dialogic, Pentium, and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

Printed on recycled paper. 01/03